# A Report on Video Compression Analysis for High Throughput Pipelined 2D Discrete Cosine Transform

Jyotishman Saikia<sup>1</sup>, Deepak Kumar<sup>2</sup>

<sup>1</sup> M.Tech. Scholar, ECE, Vidhyapeeth Institute of Science & Technology, Bhopal, India; <sup>2</sup>Assistant Professor, ECE, Vidhyapeeth Institute of Science & Technology, Bhopal, India;

Abstract – The objective of Video/image compression is to decrease inappropriateness and redundancy of the Video/image information in arrangement for store or transmit data in a capable form. Video/image compression may be lossy or lossless. Loss-less compression is preferred for real purposes and frequently for medical imaging, technical drawings, clip art, or comics. Lossy compression strategies, particularly when used at low bit rates, introduce compression artifacts. Lossy strategies are especially appropriate for natural Video/images such as images in applications wherever minor (sometimes imperceptible) loss of fidelity is suitable to attain a considerable reduction in bit rate. The lossy compression that produces imperceptible differences is also known as visually lossless. A fast algorithm rule for discrete cosine transforms (DCT)-domain Video/image resizing is accessible. To ease calculation, fast Wino grad DCTs is applied to a recently reported Video/image resizing method that make use of DCT low-pass truncated estimate. Our fast algorithm rule yields important enhancement in computational complexity over the fast algorithm of the reported method. We proposed modified carry look-ahead adder based fixed point DCT architecture.

**Keywords**: Signal processing method, precise estimation of  $L_{eq}$ , roughly observed data,

# I. Introduction

The system introduces a new DCT approximation that possesses an extremely low arithmetic complexity, requiring only 14 additions. This novel transform was obtained by means of solving a tailored optimization minimizing problem aiming at the transform computational cost. Second, we propose hardware implementations for several 2-D 8-point approximate approximate DCT methods consideration are (i) the proposed transform; (ii) the 2008 Bouguezel-Ahmad-Swami (BAS) DCT approximation; the parametric transform for Video/image compression; (iv) the Cintra-Bayer (CB) approximate DCT based on the rounding-off function; (v) the modified CB approximate DCT; and (vi) the DCT approximation proposed in the context of beam forming. All introduced implementations are sought to be fully parallel time-multiplexed 2-D architectures for 8×8 data blocks. Additionally, the proposed designs are based on successive calls of 1-D architectures taking advantage of the separability property of the 2-D DCT kernel. Designs were thoroughly assessed and compared.

The DCT is widely used in video coding and image compression such as videoconference and HDTV [2][3]. The quick algorithm for compute 2-D DCT can be

separated into two classes: (1) the method of row-column decomposition. These methods divide the DCT/IDCT into two 1-D DCT/IDCT with a transpose memory. These use I-D fast DCTi IDCT algorithm to do the row dealing out and send the results saved into a transpose memory to do exchange the row by column, and then using I-D fast DCT algorithm to do the column dealing out.(2)The not-row-column decomposition methods [6]. These strategies straight use the 2-D DCT/IDCT algorithmic rule to calculate 2-D DCT/IDCT. The cost of hardware is additional but it would like less computing stages. Plenty of analysis works are done on transmission of video streams since video has terribly difficult quality of service (QOS) necessities. A video stream is compressed by a video encoding mechanism before entering the transmitter module, particular in the values of MPEG2, JPEG2000, MPEG4, and H.264 etc. [1]. After compression the video bit rate may be drastically reduced. Effective high throughput video compression algorithms are always in great demand.

Among a variety of transform technique for image compression, the discrete cosine transform (DCT) [1] is the most popular and efficient one in realistic image and video coding application, such as high-definition television (HDTV). This is often due to the detail that it can provide an approximately best performance and may be implemented at an appropriate cost

Advanced video services have emerged as a focus of concern as the technology of digital signal processing, VLSI, and broadband networks advance. Examples of such services contain multi-point videoconferencing, interactive networked video, video editing/publishing, and superior multimedia workstations. Generally, video signals are compressed when transmitted over networks or stored in database. After video signal are compressed, there are still many situations where more manipulations of such compressed video are needed. As an example, in a multi-point video conferencing, multiple compressed video sources may need to be manipulate and composited inside the network at the so-called video bridge. without using pipelined design, only three frames per second are often processed whereas using forty five stage pipeline we are able to process forty frames per second as may be known by timing wave form info with respective to clock, this kind of application are often utilized in high processing of High Definition signal as an example in wireless High-Definition multimedia Interface (HDMI), and video post processing of HDMI.

Data compression is the technique to cut back the redundancies in information illustration so as to decrease information storage necessities and therefore communication costs. Reducing the storage requirement is similar to increasing the capacity of the storage medium and therefore communication bandwidth. Therefore the development of efficient compression techniques can continue to be a design challenge for future communication systems and advanced multimedia system applications. Information is represented as a combination of data and redundancy. Information is the portion of data that must be preserved permanently in its original kind in order to correctly interpret the means or purpose of the information. Redundancy is those portions of data which will be removed when it's not needed or are often reinserted to interpret the information when required. Most often, the redundancy is reinserted in order to get the original information in its original kind. A technique to reduce the redundancy of information is outlined as information compression. The redundancy in data illustration is reduced such the simplest way that it is often subsequently reinserted to recover the initial data, which is termed decompression of the information.

## II. Format of Manuscript

## II.1. System Architecture

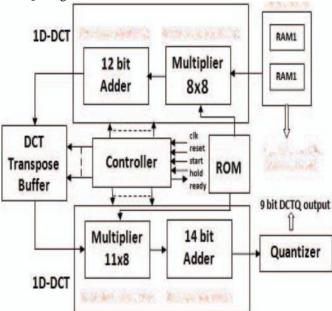

The image to be processed is input block by block by a host computer such as a Pentium Processor, into the DCTQ processor, where the discrete cosine transform is performed followed by quantization. The application is to receive a burst of image/video data and apply a transform

such as the DCT followed by quantization in order to effect compression on a picture. Fig.1 presents the block diagram for the proposed high level system design. DCTQ processor can be viewed as a black box with inputs and outputs defined to suit the application requirements. Based on the emerging details, specifications are formulated. Next the blocks used in DCTQ design will be examined.

Fig.1 Proposed high level system architecture

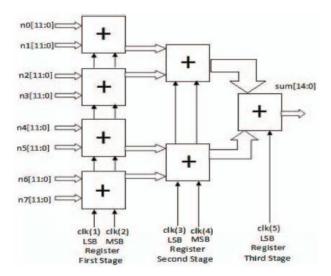

## II.2. Modified Adder

Parallel signed adder shown in Fig.2 has a simple algorithm. This has been proposed for use in the DCTQ application, where speed of processing has the top most priority. The signed addition can be realized with seven 2-input adders and five pipeline stages. In the first stage, four numbers of 12 bits, two's complement adders are used to add all the 8 numbers. They work concurrently, thereby speeding up the process.

They have pipe lined registers internally. The clock input is marked as clk (l), clk (2), etc., and correspond to internal pipeline registers. The LSBs at the first clock pulse clk (l) and the MSBs at the next clock pulse clk (2) are added along with the carry generated at the LSB. In the second stage, the four outputs are added, each of size 13 bits, generated at the first stage. Two numbers of 2-input adders are used at this stage. LSBs and MSBs are added with the arrival of the clock pulse clk (3) and clock pulse clk (4) respectively. In the third stage, with the arrival of the clock pulse clk (5), the LSBs of the two inputs of size, 14 bits are added. Subsequently, the MSBs are added along with carry generated while adding the LSBs to produce 15 bits final result.

Fig. 2 Modified Adders

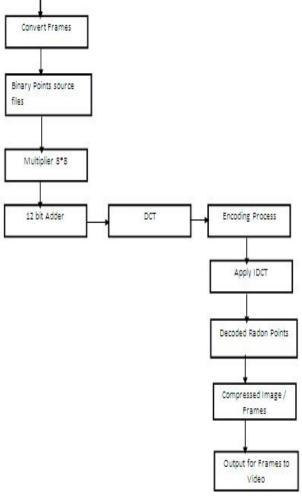

Fig.3 Flow diagram of proposed system

# III. Theory

#### III.1. Discrete Cosine Transform (DCT)

The discrete cosine transform (DCT) help divide the image into elements (or spectral sub-bands) of differing

consequence (with respect to the imagery visual quality). The DCT is all most similar to the discrete Fourier transform: it transforms a symbol or image from the spatial domain to the frequency domain.

Discrete cosines transform a technique for instead of waveform data as a biased sum of cosines. DCT is usually used for data compression, as in JPEG. This usage of DCT outcome in lossy compression. DCT itself doesn't misplace data rather; data compression technologies that rely on DCT estimated some of the coefficients to decrease the amount of data.

A discrete cosine transform (DCT) expresses a sequence of finitely several data points in terms of a sum of cosine functions oscillating at completely different frequencies. Signal information is generally targeted in an exceedingly few low-frequency elements of the DCT. Over the years, considerable amount of analysis work have been carried out in proposing new algorithms for the DCT [2, 3] and implementing them on general-purpose computers, DSPs, and ASICs. Direct 2-D approach [4] results in less parallelism, whereas separable row-column I-D approach [5] yields a quicker algorithmic rule.

#### III.2. Video Compression

Video compression techniques created feasible variety of applications [6-9]. Four distinct applications of the compressed video are often summarized as: (a) consumer broadcast TV, (b) consumer playback, (c) desktop video, and (d) videoconferencing.

An perfect video compression method should have the Following characteristics:

- Will manufacture levels of compression rival MPEG without offensive artifact.

- Can be contending back in real time with in expensive hardware support.

- Can humiliate easily under system load or on a slow platform.

- Can be compressed in real time with cheap hardware support.

It is widely used and robust method for Video/image compression, it has excellent energy compaction for highly correlated data, which is superior to DFT and WHT. Though KLT minimizes the MSE for any input Video/image, KLT is seldom used in various applications as it is data independent obtaining the basis Video/images for each sub Video/image is a non trivial computational task, in contrast DCT has fixed basis Video/images. Hence most practical transforms coding systems are based on DCT which provides a good compromise between the information packing ability and computational complexity. Compared to other independent transforms it has following advantages, can be implemented in single integrated circuit has ability to pack most information in fewer number of coefficients and it minimizes the block like appearance, called blocking artifact that results when the boundary between sub Video/images become visible

#### IV. Result

The Result analysis of the given algorithm is shown below:

Fig.4 Input Video Dataset

In the result analysis of video comperasion we see there is multiple dataset as a input video taken from our computer system. In which we have to select the one as a input data.

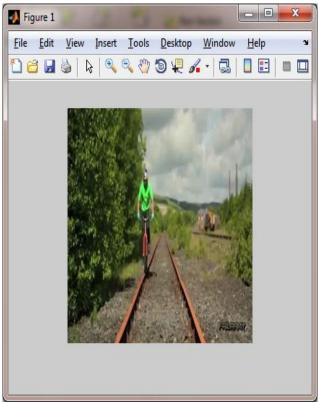

Fig. 5 Selected Input Video

In the above figure we see the frame of the selected input video. In which we applied the comperession technique on it Figure 5 shows that input video.

Fig. 6. Xilinx Tool

Xilinx Tools may be a suite of software system tools used for the design of digital circuits implemented using Xilinx Field Programmable Gate Array (FPGA) or complex Programmable Logic Device (CPLD). the design procedure consists of (a) design entry, (b) synthesis andimplementation of the design, (c) functional simulation and (d) testing and verification. Digital designs are often entered in various ways in which using the above CAD tools: using a schematic entry tool, using a hardware description language (HDL) – Verilog or VHDL or a combination of both. during this laboratory we'll only use the planning flow that involves the use of Verilog HDL.In figure six xlinix tool screen shot is shown.

TABLE 1 Comparison Table

| Logic Unit            | Present Paper | Output Result |

|-----------------------|---------------|---------------|

| NO. of Slices         | 4409          | 96            |

| No.of Slice<br>FF's   | 5322          | 96            |

| No of Bonded<br>IOB's | 98            | 153           |

## V. Conclusion

Result analysis of a linear highly pipelined, parallel algorithm and architecture has been proposed and implemented for 2D-DCT and quantization on FPGAs.

The proposed 2-D DCT core employs a single 1-D DCT core and one TMEM with a small area. Algorithms used in this technique have significant impact on the efficiency of the video operation technique. Orthogonal transform give great flexibility for following manipulation techniques in the change domain, however non-linear coding algorithms like mc do not. The close interaction between the compression algorithms and the manipulation technique powerfully inspire a joint approach to optimum algorithm designs for video compression and manipulation. in this Project conferred overflow-complexity DCT approximation obtained via The resulting approximate transforms requiresonly10 additions and possesses performance metrics comparable progressive methods, as well as the recent architecture conferred. By means that of computational simulation, VLSI hardware realizations, and a full HECV implementation, we tend to incontestable the practical relevancy of our methodology as a Video/image and video codec.

## References

- [1] Kim SeongSoo,"Adaptive multi-beam transmission of uncompressed video over 60ghz wireless systems" in International journal of Future Generation Communication and ssNetworking, 12/2007.

- [2] P. Lee and F. Y. Huang, "An efficient prime-factor algorithm for the discrete cosine transform and its hardware implementations", IEEE Trans. Signal Process., 42, pp.1996-2005, 1994.

- [3] C.L. Wang and C.Y.Chen, "High throughput VLSI architectures for the I-D and 2-D discrete cosine transfonns", IEEE Trans. Circuits Syst. Video Technol., 5, pp. 31-40, 1995.

- [4] Yung-Pin Lee, Thou-Ho Chen, Liang-Gee Chen, Mei-Juan Chen and Chung-Wei Ku, "A cost-effective architecture for 8 x 8 2-D DCT//DCT using direct method", IEEE Trans. Circuits Syst. Video Technol., 7, 1997.]

- [5] Yi-Shin Tung, Chia-Chiang Ho and Ja-Lung Wu," MMX-based DCT and MC Algorithms for real-time pure software MPEG decoding", IEEE Computer Society Circuits and Systems, Signal Processing, 1, Florence, Italy, pp. 357-362, 1999.

- [6] Y.P. Lee, T.H. Chen, L.G. Chen, MJ. Chen and C.W. Ku, "A cost-effective architecture for 8 x 8 2D-DCT//DCT using direct method", IEEE Trans. Circuits Syst. Video Technol., 7, pp. 459-467, 1997.

- [7] D.V.R. Murthy, S. Ramachandran and S. Srinivasan, "Parallel implementation of 2Ddiscrete cosine transforn using EPLDs", International Conference on VLSI Design, Goa, January, 1999.

- [8] S. Ramachandran, S. Srinivasan and R. Chen, "EPLD-based Architecture of Real Time 2D-Discrete Cosine Transform and Quantization for Image Compression", IEEE International Symposium on Circuits and Systems (ISCAS '99), Orlando, Florida, May-June 1999.

- [9] Trang T.T. Do, Binh P. Nguyen "A High-Accuracy and High-Speed 2-D 8x8 Discrete Cosine Transfonn Design". Proceedings of ICGCRCICT 2010, vol. 1, 2010, pp. 135-138.

- [10] L Basri, B. Sutopo, "Implementation ID-DCT Algoritma Feig-Wino grad di FPGA Spartan-3E (Indonesian)". Proceedings of CITEE 2009,vol. 1, 2009, pp. 198-203

- [11] L. Agostini, S. Bampi, "Pipelined Fast 2-D DCT Architecture for JPEG Image Compression". Proceedings of the 14th Annual Symposium on Integrated Circuits and Systems Design, Pirenopolis, Brazil. IEEE Computer Society 2001. pp 226-231.

- [12] Sun, M., Ting C., and Albert M., "VLSI Implementation of a 16 X 16 Discrete Cosine Transforn", IEEE Transactions on Circuits and Systems, Vol. 36, No. 4, April 1989.

- [13] Enas Dhuhri Kusuma, Thomas Sri Widodo "FPGA Implementation of Pipelined 2D-DCT and Quantization Architecture for JPEG Image Compression" IEEE, 2010.

- [14] ISO/IEC MPEG 2 standards for generic coding of moving pictures: part 2, Video, 1988.

- [15] Ramachandran S, "Development of Algorithms and Verification Using High Level Languages" in "Digital VLSI Systems Design"., Springer, 2007.