# A Review Report on Design of Fast FIR Filter Using Compressor and Carry Select Adder

Pooja Rai<sup>1</sup>, Sanjeev shrivastava <sup>2</sup>, Dr.Mohit Gangwar<sup>3</sup>

<sup>1</sup> M.Tech Scholar, RKDF College of Engineering, Bhopal, excelpooja248@rediffmail.com, India; <sup>2,3</sup> Asst. Professor, RKDF College of Engineering, Bhopal, sanjeev.dabbu@gmail.com, mohitgangwar@gmail.com, India:

Abstract – Designing of power-efficient and high speed digital logic systems is very crucial task. Numbers of adders are designed and supply tradeoffs between power, delay and space. The carry propagation delay and space of carry select adder is reduced by splitting carry select adder into equal bit groups. In [1] to extend speed, whereas doing the multiplication or addition operations, has perpetually been a basic demand of planning of advanced system and application. Carry select Adder (CSLA) is one of the quickest adders employed in several data-processing processors to perform quick arithmetic functions. From the structure of the CSLA, it's clear that there's scope for reducing the area and power consumption in the CSLA. In this paper review/survey of previous work related to Fast FIR filter compressor and carry select adder.

**Keywords**: Ripple Carry Adder (RCA), Carry Select Adder (CSA), Excess-1 converter, Compressor, FIR Filter

#### I. Introduction

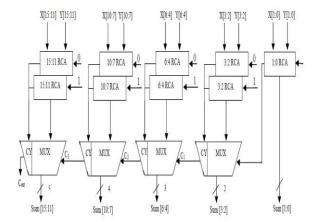

Binary addition could be a basic operation in most Digital Circuits. There are a range of adders, every has certain performance. In digital adders, the speed of addition is restricted by the time needed to propagate a carry through the adder. Every form of adder is selected depending on where the adder is to be used [1]. For high speed arithmetic operation carry select adder is often used [4]. To increase portability of systems and battery life, area and power are the critical factors of concern. It is composed of 2 four-bit ripple carry adders per section each sum and carry bits are calculated for the 2 alternatives of the input carry, "0" and "1". Addition could be a basic arithmetic operation that's generally employed in several VLSI systems, like applicationspecific digital signal process (DSP) architectures and microprocessors [3]. 16 bit Carry select adder has such three sections with one 4-bit RCA as very first section. The very first section has a carry in of zero. The linear carry-select adder is creating by change a number of equal-length adder stages. The carry out of every section determine the carry in of the subsequently segment, which after that select the suitable ripple carry adder. The several projected procedure achieve high performance with reduced area & power [3]. Finite Impulse Response (FIR) filter has been designed by considering the power consumption in multiplier unit and adder unit. Design of VLSI circuit with less area and high speed has become a main concern for digital designers [5]. Designing area

economical VLSI systems has emerged as extremely in demand due to the quick growing technology in mobile communications and computation. There are differing types of Adder styles are projected and implemented to cut back the facility consumption. To realize additional speed CSLA is replaced by SQRT CSLA [5]. The CSLA is employed for procedure systems to alleviate the matter of carry propagation delay by separately generating multiple carries then choose a carry to search out the sum. Whereas planning the high performance digital systems like microprocessors, FIR filters and digital signal processors etc., the multiplier factor is one among the necessary key hardware blocks. several researchers have work hard and try to design multipliers which provide either high speed, consume low power, generates regular layout and utilizes the less area or maybe combination of them, in order that they will be appropriate for numerous compact, low power and high speed VLSI implementations however area and speed are 2 conflicting constraints.

#### II. Literature Review

Deepak Kumar Patel et. al. [1] "Design of Fast FIR Filter Using Compressor and Carry Select Adder" In this paper, author propose a method for planning of FIR filter using multiplier factor supported compressor and carry select adder. Speed and area are currently a day's one

among the basic style problems in digital era. Carry select Adder (CSA) may be a quickest adder employed in several processors to accomplish quick arithmetic performs. Proposed modified Adder is a simple technique used in this paper to decrease the delay of Carry Select Adder. By using this multiplier and modified CSA, a FIR filter is implemented and our proposed FIR filter improves the performance of system.

Raksha Chouksey et. al. [2] "An Efficient and Fast VLSI Architecture for Carry Select Adder" In this paper, author present an inventive CSA architecture. Verification of our proposed design is done through design and implementation of 16, 32 and 64 bit adder circuits.CSA is one of the highest speed adders employ in numerous processors to perform fast arithmetic operations. Appropriate high speed adder structural design turns into essential. More than a few adder structural designs have been developed to increase the efficiency of the adder. A simple technique is proposed in this paper to reduce the delay of Carry Select Adder. The regular CSA has a disadvantage of large chip area and larger delay. The technique which is discussed in this paper reduces area and delay when compared to both previous CSA.

Gowrishankar V et. al. [3] "Efficient FIR Filter Design Using Modified Carry Select Adder & Wallace Tree Multiplier" In projected work multiplier unit high speed is realizing by means of XOR-XNOR column by column diminution compressors as an alternative of compressors using full adder. The power & delay assessment is performing for both existing and proposed method of FIR filter. In this paper the FIR filter is designed to increase the speed of addition and decrease the power taken by the multiplier unit. The carry propagation delay and area of carry select adder is reduced by splitting carry select adder into equal bit groups. The delay of FIR filter gets increased for lower order tap and reduced statically when go for higher order tap of FIR filter. The compared results prove that proposed carry select adder with binary to exess-1 converter performs faster than conventional carry select adder.

A. Ramana Kumari et. al. [4] "Implementation of Low-Power and Area-Efficient Carry Select Adder" This work uses an easy and economical gate-level modification to considerably cut back the area and power of the CSLA. supported this modification 8-, 16-, 32-, and 64-b square-root CSLA (SQRT CSLA) design are developed and compared with the regular SQRT CSLA design. The projected design has reduced area and power as compared with the regular SQRT CSLA with only a small increase within the delay. The results analysis shows that the projected CSLA structure is best than the regular SQRT CSLA. easy approach is projected in this paper to scale back the area and power of SQRT CSLA design. The changed CSLA design is therefore, low area, low power, easy and economical for VLSI hardware implementation.

Gyanesh Savita et. al. [5] "Designing of Low Power 16-Bit Carry Select Adder with Less Delay in 45 nm CMOS Process Technology" This work uses an easy and an economical gate-level modification using 45nm CMOS method Technology, that drastically reduces the area and delay of the CSLA. Designing of power-efficient and high speed digital logic systems is extremely crucial task. Numbers of adders are designed and provide tradeoffs between power, delay and area. The projected design has reduced area and delay to an excellent extent compared with the previous CSLA developed in 180 nm. A simple dual comparison has been proposed in this paper with reduction in the Area, Power and Delay of CSLA architecture.

Prajakta S. Wasekar et. al. [6] "An Area Efficient Carry Select Adder using Binary Excess Converter" In this work a completely unique carry select adder exploitation Binary Excess convertor (BEC) is projected. Adders are one among the widely used digital elements in digital integrated circuit style. A ripple carry adder has smaller area but less speed. A carry look-ahead adder is faster though its area necessities are high. An easy approach is projected in this paper is to cut back the area and power consumption of CSLA architecture. The modified CSLA architecture is thus, low area, low power, easy and efficient for VLSI hardware implementation.

# III. Method

## III.1. Logic Design Styles

Adder is that the most ordinarily used arithmetic block of the Central process Unit (CPU) and Digital Signal process (DSP), thus its performance and power optimization is of utmost importance. Static logic circuits are those which might hold their output logic levels for indefinite periods as long because the inputs are unchanged. Every logic stage contains pull up and pulls down networks controlled by input signals. Since the pull up and pull down networks are never 'on' at the same time, there's no static power consumption. For arithmetic applications, 3 totally different logic designs are used for a full adder design to realize best performance results for adder design.

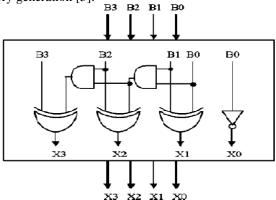

## III.2. Binary Excess Converter (BEC)

Binary to excess convertor is employed to cut back the area and power consumption in Carry select Adder. The most plan of this work is to use BEC rather than the RCA with Cin=1 so as to cut back the area and power consumption of the regular CSLA. The most advantage of this BEC logic comes from the lesser variety of logic gates than the n-bit Full Adder (FA) structure.

## III.3. 16-BIT CONVENTIONAL CARRY SELECT ADDER

16 bit conventional carry select adder is explained with the help of detailed block diagram which is shown in figure 2. We have separated our structure in different sizes like 2bit, 3 bit, 4 bit and into 5 bit blocks of Ripple Carry Adder. The RCA is simplest adder but their working performance is restricted due to the method of carry generation [5].

Fig 1.: Binary Excess Converter

Figure 2: 16-Bit Carry Select Adder using Ripple Carry Adder [1]

### IV. Conclusion

In this paper review of Fast FIR Filter Using Compressor and Carry Select Adder and related work should be studied. In [1] author propose a technique for designing of FIR filter using multiplier based on compressor and carry select adder. Proposed modified Adder is a simple technique used in this paper to decrease the delay of Carry Select Adder. In [2] present an innovative CSA architecture. A simple technique is projected in this paper to cut back the delay of Carry select Adder. The area-delay products of our projected design show a decrease for 16-bit, 32-bit and 64-bit sizes which shows the success of the projected style.

#### References

Deepak Kumar Patel, Raksha Chouksey, Dr. Minal Saxena "Design of Fast FIR Filter Using Compressor and Carry Select Adder" 2016 3rd International Conference on Signal Processing and Integrated Networks (SPIN)

- [2] Raksha Chouksey, Neha Verma "An Efficient And Fast VLSI Architecture For Carry Select Adder" International Journal of Engineering Research-Online Vol.3., Issue.3, 2015

- [3] Gowrishankar V, Manoranjitham D, Jagadeesh P " Efficient FIR Filter Design Using Modified Carry Select Adder & Wallace Tree Multiplier" Intern. Jour. of Science, Engineering and Technology Research (IJSETR) Volume 2, Issue 3, March 2013ISSN: 2278 – 7798

- [4] A. Ramana Kumari, B. Sumalatha "Implementation of Low-Power and Area-Efficient Carry Select Adder" Intern. jou. of scientific engineering and technology Research, Vol. 03 issue 33 October 2014, 6538-6542

- [5] Gyanesh Savita, Vijay Kumar Magraiya, Gajendra Kulshrestha, Vivek Goyal "Designing of Low Power 16-Bit Carry Select Adder with Less Delay in 45 nm CMOS Process Technology" International Journal of Emerging Technology and Advanced Engineering Volume 3, Issue 7, July 2013

- [6] Prajakta S. Wasekar "An Area Efficient Carry Select Adder using Binary Excess Converter" Imperial Journal of Interdisciplinary Research (IJIR) Vol-2, Issue-10, 2016 ISSN: 2454-1362

- [7] B. Ramkumar, H.M. Kittur, and P. M. Kannan, "ASIC implementation of modified faster carry save adder" Eur. J Sci. Res., vol. 42, no. 1, pp. S3-S8, 2010.

- [8] R. Uma, M. Mohanapriya, Sharon Paul, "Area, Delay and Power comparison of adder topology" International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.1, February 2012.

- [9] V.G. Oklobdzija, "High-Speed VLSI Arithmetic Units: Adders and Multipliers" in "Design of High-Performance Microprocessor Circuits", Book edited by A. Chandrakasan, IEEE press, 2000.

- [10] Sushma R. Huddar and Sudhir Rao Rupanagudi Kalpana M. "Novel High Speed Vedic Mathematics Multiplier using Compressors" 978-1-4673-5090-7/13/\$31.00 ©2013 IEEE